The E-INK ED050SC3 and ED060SC4 e-papers used in the e-paper experiment set require 15 signal lines, including the data bus and control signals. We also need a few more signal lines, including control of the power supply. For this reason, about 20 GPIO pins are needed to control the e-paper with a microcontroller.

When you try to use the ESP-WROOM-02, which is a convenient microcontroller that can connect to the Internet, the IO pins are too few and cannot be controlled. Therefore, the e-paper experimental set is controlled by converting the SPI signal to a 16-bit parallel signal using a shift register.

When expanding functions such as adding more switches or performing detailed power supply control on a microcomputer with only a few IOs, a general-purpose logic IC such as the 74HC595 or an IO expander IC such as the PCF8575 may be used in large numbers, but the scale of the circuit will become large.

In addition, the SPI of ESP-WROOM-02 runs at 40MHz, but the GPIO only outputs a few MHz. The resolution of the e-paper is 800x600 dots, which is a huge amount of data, so GPIO control is limited in drawing speed, and we would like to improve it a little more.

Small CPLD 5M160Z

CPLD may be able to solve these problems. CPLDs are like logic ICs that can be designed freely, for example, a 20-bit shift register or a circuit that produces pulses every 8 clocks, to create an original digital IC. What's more, it's as easy as programming into a microcomputer.

FPGAs are almost the same IC as CPLDs, but FPGAs are over-specified for this scale because of their high performance: they build large circuits, use a large number of IOs, run at ultra-high speed, and require expensive components. CPLD is the solution for those times when you want a little bit of original logic circuitry.

Intel MAX V Series

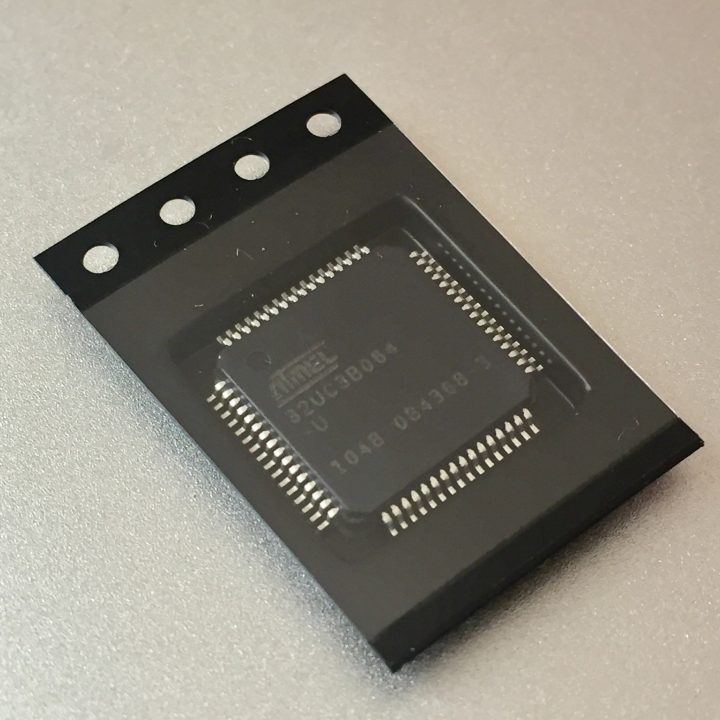

I was looking for an affordable CPLD in a 44 to 64-pin QFP package for a few hundred yen and found Intel's MAX V series.

The package is a 64-pin, 0.4mm pitch EQFP. The device with the most circuits in this package will be the 5M160Z.

It contains 128 macrocells, so it can make a maximum of 128-bit counters, right?

54 IO pins

For a 64-pin package, the maximum number of IOs is 54. For this application, about 30 pins are sufficient.

Power supply is 1.8V

Current devices are power efficient, and this device operates at a core voltage of 1.8V. When I made the AVR32 board, the core voltage was also 1.8V.

The AVR32 has a 1.8V regulator built into the microcontroller, but the MAX V does not have it. You'll need to prepare your own.

IO can be freely configured with built-in level shifter

The core is fine at 1.8V, but I want the IO to run at 3.3V. MAX V contains a level shifter and operates as an IO of the supply voltage by preparing a power supply for the IO. It supports voltages of 3.3 V, 2.5 V, 1.8 V, 1.5 V, and 1.2 V, so the core can operate at 1.8 V but the IO can operate at 3.3 V.

Design of the evaluation board

I tried to find a 5M160 evaluation board on the market, but I couldn't find one. If I don't have one, make one.

Types of pins

According to MAX® V Device Family Pin Connection Guidelines material, they are categorized as follows.

- Core power supply pin (VCCINT)

2 pin and supply 1.8V - IO power supply pin (VCCIO[1:2])

The IO pin is divided into two main banks, and each bank can be set individually for the IO voltage. For example, Bank 1's IO can be used at 3.3V and Bank 2's IO at 2.5V. This time, both are designed at 3.3V. - GND

There is no GND pin and the pad on the back of the IC is set to GND. It's difficult to implement with hand-soldering. - Clock (CLK[0:3])

This pin is used to connect an external clock when you want to use a clock inside the CPLD. Can also be used as a general-purpose IO. Since MAX V has a built-in Clock, it is a feeling to use it when an accurate Clock is needed. - JTAG pin

Pull down with TCK 1 kΩ

Pull up with TMS 10 kΩ

Pull up with TDO 10 kΩ

TDO No particular indication (if you look at various circuits, they are often pulled up) - Reset Pin (DEV_CLRn)

By setting this pin in advance, it becomes a pin that resets the device when it is low. Can also be used as a general-purpose IO. The document recommends that you pull down if you don't want to use it as either feature. - Enabling pin (DEV_OE)

If you set this setting in advance, all the output pins can be set to high impedance at low. Can also be used as a general-purpose IO. The document recommends that you pull down if you don't want to use it as either feature. - IO Pin

Some pins are capable of differential operation. (I don't request that much this time)

Block diagram

Using USB as the power supply, power with 3.3V and 1.8V regulators. After that, I will output JTAG and IO for each bank to the connector. It's very simple.

Schematic

Draw a schematic with KiCad. For the 3.3V regulator, I used ADP3338 which is a low-drop regulator that I also used when I made the AVR32 board. I used the XC6206 1.8V regulator for the 1.8V. This regulator only needs a drop of 250mV at 100mA output. It can be used stably even if it generates 3.3V to 1.8V.

After that, I put 4 LEDs for operation check.

Artwork

I wired the power supply manually and left the rest to Ortreater. It wasn't so difficult, and it took only a few ten minutes to finish. Manually shape the wiring results of the Ortreater. This shaping takes a lot of time.

Imposition

I'll be ordering SeeedStudio's FusionPCB again this time. Since two evaluation boards can be taken in the size of 10cmx10cm, I will imposition them with pcbnew.

Orders

Order boards and stencils to SeeebStudio. I was able to order a little cheaper because using a discount coupon at the end of March gives you a 20% discount.

You can get a discount if you enter "Fusion 20" when ordering. The shipping cost did not come cheap.

I've also ordered some parts, so I'd like to make them when they arrive. I think it's about three weeks away.

It arrived on April 16, 2019. Continue reading

The CPLD experiment set made here can be purchased here.